Started coding for DDS (Direct Digital Synthesis) of the FSK audio signal. I won't use DMA (as hinted before): no need to spare MCU cycles, it won't have much computation to do. Each samples will be from a pre-calculated value table (aka LUT, Look Up Table) and submitted to the DAC at regular interval.

Hypothesis: sampling frequency of the DAC output can be the same (but not less) as the sampling frequency of the audio recorders input, ie 48 kHz. [EDIT: wrong! this equivalence introduces too much quantization errors even after going trhough a low pass filter (passive RC), see below]

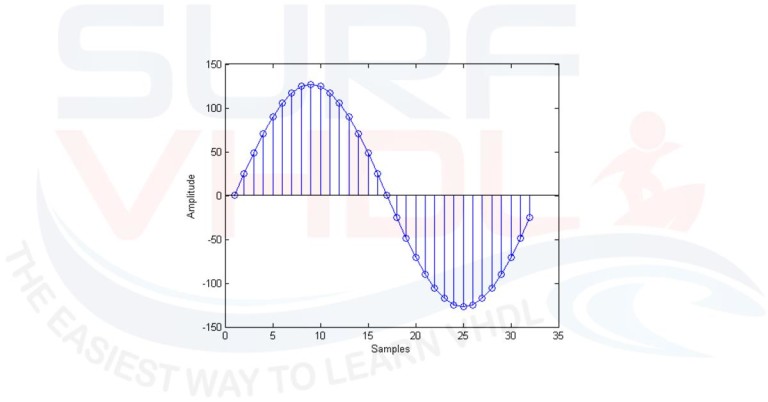

So samples are produced at 20.8 μS intervals. The mark frequency (the highest) is 2.1 kHz (one cycle in 476 μS) so it will need 23 calculated values, rounded up to 32 in the LUT (as in the figure above). Note: the SAMD21 is clocked at 48 MHz, so there are 1000 clock cycles between DAC samples... almost enough time to take a nap.

Comments

Post a Comment